# A 93DB GAIN AND LOW POWER OPERATIONAL TRANS CONDUCTANCE AMPLIFIER FOR DATA CONVERTERS

E.Srinivas<sup>1</sup>, Ch.Karuna Sree<sup>2</sup>, B.Kavya<sup>3</sup> Anurag Group of Institutions

### Abstract

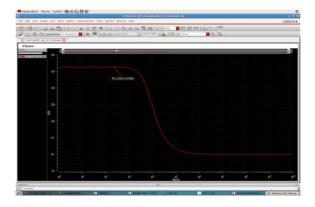

This paper presents a design to achieve Low power and High gain of an Operational Transcondcutance Amplifier simultaneously. The small-signal voltage gain, unity gain bandwidth of the conventional operational amplifier are improved in this proposed design. This proposed design uses a positive feedback technique, which is not usually preferred due its uncontrollability. The simulated results of the circuit show DC gain of 92.8 dB, unity gain bandwidth of 93.3MHz, phase margin of 71.6°, power supply of the proposed operational amplifier is 1.8 V (rail-to-rail ±700 mV), and power consumption is 266uWatts. This circuit specification has encountered the requirements of A/D Converter.

Keywords: Gain enhancement, positive feedback, differential amplifier, OTA(Operational Trans conductance Amplifier), small-signal Analysis

### I. INTRODUCTION

In CMOS technology, the size for the gate channel length of complementary MOS transistors has been reduced from micrometres to submicron, which is known as short channel. One of the most problematic issues with integrated circuit (IC) is scaling down the gate channel length of the transistor devices for lowvoltage, which poses a significant problem for Analog circuits. Scaling down devices to submicron or smaller levels means lowering the output resistance of the MOSFET; as a result, the small-signal gain of the differential pair is reduced.

To recover that small-signal gain, the output resistance is increased by arranging the MOSFET devices vertically, which this is known as cascode. Cascoding increases the differential gain significantly, but it also causes a reduction in the overhead voltage. Consequently, this reduces the output signal swings of the differential amplifiers.

This paper addresses the problems of gain decrease and unity gain bandwidth reduction by providing a positive feedback to the cross-coupled differential pair. The laterally configured amplifier circuit increases the smallsignal voltage gain and also preserves the higher output voltage swings.

### **II.CMOS OPERATIONAL AMPLIFIER**

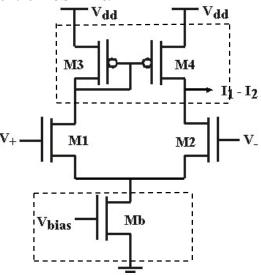

The circuit in Fig. 1 shows the conventional CMOS operational amplifier(Op-amp) which provides a very high gain practically. The gain of the amplifier depends on the output resistance of PMOS and NMOS transistors and the transconductance of the circuit. The output resistance in turn depends on the channel length of the MOSFET's.

Figure 1 A Conventional Differential amplifier

The biasing circuit and current mirror are highlighted which make work the differential pair. The gain of the above Op-amp can be written as

$A_V g_{m1,2} r_{on} \| r_{op} \|$

From [1], the relationship between output resistance and channel length (L) of a MOSFET device operating in saturation region is

$$r_o \propto \frac{L^2}{V_{DS,sat}^2}$$

We can observe that when the length is reduced, the total output resistance of the circuit reduces and the gain follows.

(2)

### **III.POSITIVE FEEDBACK SYSTEM**

Positive feedback technique is not preferred over the negative feedback technique due its unstable and uncontrollable nature. When designed properly, a positive feedback gives more yields when compared to negative feedback. Positive feedback enhances the gain of the circuit overcoming the degradation due to down-scaled technologies.

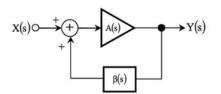

The positive feedback system is shown in Figure 2. The quantity A shows the feed forward amplifier network with a gain of A(s) where as B shows the positive feedback circuit with a gain of  $\beta(s)$ .

Figure 2 Positive feedback system

(3)

The closed loop transfer function is given as

$$\frac{\mathbf{Y}(\mathbf{s})}{\mathbf{X}(\mathbf{s})} = \frac{\mathbf{A}(\mathbf{s})}{1 - \mathbf{A}(\mathbf{s}) \cdot \boldsymbol{\beta}(\mathbf{s})}$$

The  $A(s).\beta(s)$  term is the "loop gain" of the system. The loop gain values must be greater than zero but less than one to ensure the

feedback is positive. When the loop gainA(s). $\beta$ (s) is equal to one, the denominator of (3) becomes zero; thus, the value of the transfer function Y(s)/X(s)becomes infinity. At this point, the pole is moved to the right-half plane, and the circuit becomes unstable. Also, designing too close to the origin of the axes is not recommended because of the instability concern.

## IV.GAIN ENHANCEMENT CROSS COUPLED DIFFERENTIAL AMPLIFIER

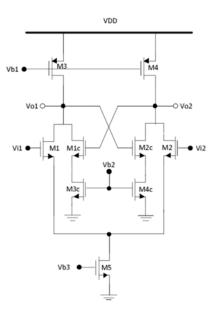

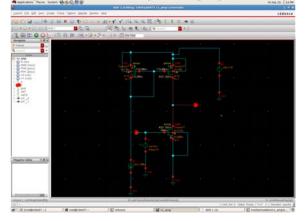

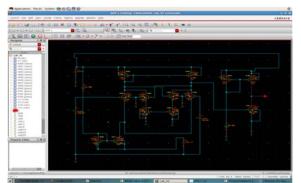

The proposed circuit for gain enhancement using positive feedback concept is shown in Figure 3. The proposed circuit is fully-symmetric differential amplifier, which MOS transistors cross-coupled had "horizontal" way rather than "vertical", and it generates a negative transconductance, -gm. This negative gm cancels out the already existing transconductance due to PMOS load transistors and NMOS differential pair. A very high DC gain is assured due to this.

To analyse the small-signal gain of the proposed circuit, let us focus on the differential pair with positive feedback circuit as shown in Figure 3.

Figure 3 Cross-coupled diff amp with positive feedback

#### INTERNATIONAL JOURNAL OF CURRENT ENGINEERING AND SCIENTIFIC RESEARCH (IJCESR)

The total transconductance of the circuit is given by

$$G_{\rm m} = \frac{I_{\rm o}}{V_{\rm glc}} = \frac{I_{\rm o}}{V_{\rm o2}}$$

The output resistance of the given circuit can be calculated as

(4)

$$R = \frac{v_{o1}}{I_o} = \frac{v_{o1}}{G_m v_{o2}} = \frac{-v_{o2}}{G_m v_{o2}} = -\frac{1}{G_m}$$

(5)

The small-signal gain is given by

$$A_{d} = \frac{V_{o2} - V_{o1}}{V_{id}} = g_{m1} \cdot (r_{o1} \parallel r_{o3} \parallel R_{o} \parallel R)$$

(6)

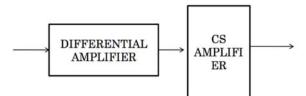

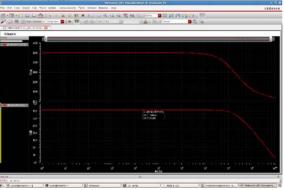

### V.COMMONSOURCE AS THE OUTPUT STAGE

To increase the output resistance of the entire system, common source amplifier is used as the output stage. This increase in outputs resistance increases the overall gain further and increases the sustainability of the circuit.

Figure 4 Blocked diagram of proposed design

Figure 5 Common source Amplifier

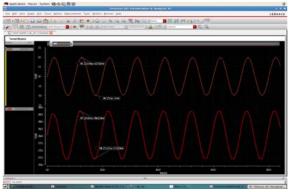

Figure 8 Gain and Phase plot of operational Transconductane Amplifier

Figure 9 Schematic of the OTA design in common mode

### INTERNATIONAL JOURNAL OF CURRENT ENGINEERING AND SCIENTIFIC RESEARCH (IJCESR)

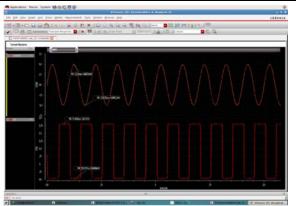

Figure10 AC response of the circuit in common mode

Figure11 Transient response of the circuit in common mode

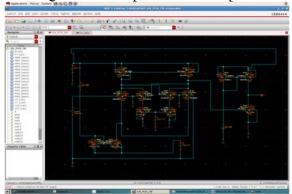

Figure 12 Schematic of the differential mode of the circuit

Figure 13 AC response in differential mode

Figure 14 Transient response of the OTA circuit

| Table      | 1:Comparison | of | desired | specifications |

|------------|--------------|----|---------|----------------|

| Vs Results |              |    |         |                |

| Parameters   | Desired<br>Specifications | Results   |

|--------------|---------------------------|-----------|

| Power supply | ±1.8v                     | ±1.8v     |

| Technology   | 180nm                     | 180nm     |

| Gain         | >= 90dB                   | 92.8dB    |

| UGF          | 100MHz                    | 93.3MHz   |

| CMRR         | >= 80dB                   | 96.06dB   |

| Power        | >100µWatts                | 266µWatts |

| consumption  |                           |           |

| Phase Margin | 60°                       | 71.6°     |

### **V.CONCLUSION**

The Operational Transconductance Amplifier has been designed and its behavior is analyzed. Simulation results confirm that the proposed design procedure can be utilized to design op amp. The simulation is done with cadence virtuoso Software. The design is on 0.18µ CMOS Technology. The Op amp is designed with low power of 266µw and gain of 92.8dB and gain bandwidth of 93.3MHz. Design of accurate A/D converters and filters are challenging work for present applications. So this work can be extended further for communication applications with improved slew rate .For the mixed integrated circuit unity gain bandwidth can be further increased.

### REFERENCES

- [1] P.E. Allen and D.R. Holberg, "CMOS Analog Circuit Design" Oxford University Press, 2nd edition.

- [2] D. A. Johns and K. Martin, "Analog Integrated Circuit Design," New York: John Wiley & Sons, Inc., 1997.

#### INTERNATIONAL JOURNAL OF CURRENT ENGINEERING AND SCIENTIFIC RESEARCH (IJCESR)

- [3] Amana Yadav, "A Review Paper On Design And Synthesis Of Two stage CMOS Op-amp" ©Ijaet Issn: 2231-1963677 Vol. 2, Issue 1, Pp. 677-688

- [4] B. Razavi, "Design of Analog CMOS Integrated Circuits," Tata McGraw-Hill, 2002.

- [5] Ankit Sharma, Parminder Singh Jassal. ,"Design Of A Ultra Low Power, High Precision CMOS Opamp Based Comparator For Biomedical Applications", International Journal of Engineering Research and

- [6] Applications (IJERA) , Vol. 2, Issue 3, May-Jun 2012, pp.2487-2492

- [7] R Lotfi, M Tahenadeh-Sani, M Yaser Asizi, and 0. Shaaei. ,"A 1-VMOSFET-only Fully Differential Dynamic Comparator Used in Low Voltage Pipe Lined AID Convertor,"

- [8] Ehsan Kargaran, Hojat Khosrowjerdi, Karim Ghaffarzadegan ,"A 1.5 V High Swing Ultra- Low-Power Two Stage CMOS OP-AMP in 0.18 μmTechnology ," 2010 2nd International Conference on Mechanical and Electronics Engineering (ICMEE 2010).

- [9] Purvi .D Patel, Kehul . A Shah "Design of low power two stage CMOS Operational Amplifier".(IJSR)ISSN23197064.

- [10] P.K.Sinha, Abhishek Vikram, Dr. K.S.YADAV, "Design Of Two Stage CMOS Op-amp With Low Power And High Slew Rate." (IJERT) Vol. 1 Issue 8, October - 2012

- [11] Priyanka Kakoty, "Design of a high frequency low voltage CMOS operational amplifier", International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.1, March 2011

- [12] Sannella, M. J. 1994 Constraint Satisfaction and Debugging for Interactive User Interfaces. Doctoral Thesis. UMI Order Number: UMI Order No. GAX95-09398., University of Washington.

- [13] Forman, G. 2003. An extensive empirical study of feature selection metrics for text classification. J. Mach. Learn. Res. 3 (Mar. 2003), 1289-1305.

- [14] Brown, L. D., Hua, H., and Gao, C. 2003. A widget framework for augmented interaction in SCAPE.

- [15] Y.T. Yu, M.F. Lau, "A comparison of MC/DC, MUMCUT and several other coverage criteria for logical decisions",

Journal of Systems and Software, 2005, in press.