# ULTRA-THIN FLEXIBLE PACKAGING USING CMOS RF INTEGRATED CIRCUITS

T.SRAVAN KUMAR, M. CHANDRA SHEKER, JATROTH SRINIVAS 4.CH.SPANDANA, 5.RAVI KUMAR ANAND

> Assistant Professor, Department of ECE Ellenki College of Engineering and Technology thoutireddy 76@yahoo.co.in

Abstract— For the first time, this Report introduces RF compatibility studies for the next-generation wireless communication processes requiring compatible body systems, in the form of fully integrated CMOS RF integrated circuits, where wireless Communication RFICs are integrated in ultra-thin compact packets. As the test case, the RF properties of a various die substrate thickness **CMOS** (VCO) chip determined and the results were analysed. The studied CMOS VCO chip has been developed and manufactured using the RF-CMOS 180 nm method. The reliability of VCO chips efficiency is characterised and the results comparable between 250 and 50, 35 and 25 µm are correlated before and after diet. The study shall take account of critical RF efficiency parameters, such as oscillation frequency, output power and phase ring. All die-cells are positioned face-up in the micro chamber of the probe station to be sampled on a metal chuck with connector. Due to the effects on the diminishing diet, the phase noise degradation is seen significantly when the variations in frequency and output power are  $\pm 1\%$  and  $\pm 1$  dB respectively. The very well fact of phase noise sensitivity to the thickness of the substrate due to leakage supports this and SOI CMOS is commonly debated in order to mitigate this parasite.

Keywords—radio frequency (RF), complementary metal oxide semiconductor (CMOS), voltage controlled oscillator (VCO), ultra thin flexible packages, frequency of oscillation, output power, phase noise

# I. INTRODUCTION

The electronic devices of next century drive the technology sector to include ultra-thin and modular integrated circuits (ICs). Using ultra-thin and compact ICs, efficient and cost-effective technologies have an influence on many applications such as cellular, portable electronics, the Internet of Things and health care surveillance. The impact of die-substrate thinners on the RF efficiency of an IC is one of the key challenges to achieve versatile and ultrathin ICs. There are also problems associated with the implementation of incredibly slim ICs because the ultra-thin ICs need to be handled accuracy with great and because thinning would likely cause die-substrata electrical efficiency deterioration. Due ultra-thinning the functional areas of incredibly thin IC can be weakened and thus the general performance of the ICs can be affected. The various facets of IC substrata are seen to dilute much of the previous work, but only to 40 um. Much is based on efficiency of electrostatic discharge, thermal characterisation ultra-thin chip modeling. Although the effects of reduction of the plate thickness on an RF transformer are examined, the total RF output effects of a fully integrated RFIC were not previously studied by the substrate dilution.

This Letter introduces for the very first time in its best understanding RF statistical analyses of integrated RFIC CMOS chips with different die thicknesses up to 25  $\mu$ m for ultra thin flexible semiconductor materials. As a test case, the research and review were done with fully integrated VCO chips which were developed and

manufactured using the 180-nm CMOS process. Measuring in this work has been carried out to assess the effect of significant VCO parameters including operating frequency, RF output, phase noise and DC efficiency due to dilution in the substratum.

# II. VCO CHIPS THINNING AND CHARACTERISE.

On the regular die the die, the phase of CMOS is approximately 250- to 300 µm micrometers. Figure 1 shows a substrate layer thickness of one micrometer in 1-micron CMOS-6-180nm CMOS 180nm technology, which is 1 µm thick. For ultra-thin flexible, ultra-thin electronics, LC-output VCOs were considered stronger. Twenty chips are often used in order to allow for die-to-to-edge difference and calculation error. When working with the die, variations thickness die same homogenised. In the first step, the input stage of a synthesizer circuit, twenty VCO chips are studied with respect to frequency spectrum, RF output power, RF output amplitude, and phase noise.

In the second stage, 20 thin and dice chips are diced into four separate die-sub tier thicknesses: thin chips with 50-µm substrate, thin chips with 35-µm substrate, thin chips with 16.5-µm, and thin dice chips with a 25-µ thickness. Each thinned die is fixed on a thermal-release wafer, and has a temporary handle for assembly with ultra-thin ICs added for use in a process just in case.

FIG. 1 THE FOLLOWING PICTURE SHOWS THE LAYERED MAP FOR A 1-POLY 6-METAL 180 NM CMOS PROCESSING TECHNOLOGIES (THE FIGURE IS NOT TO SCALE).

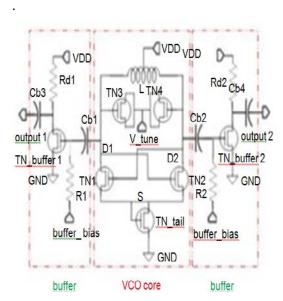

The buffer-phase structure of the VCO is shown in Fig. 2 adjusting the frequency with the movable condenser; two NMOS transistors (TN3 and TN4) are used. To provide performance separation required in order to increase control performance of VCO and also for 50 to meet output impedance, a common-source blocker is used.

Fig 2 circuit schematic

#### III. CHARACTERISTICS

The Tektronix RSA3408B spectrum analyser was used to characterise all VCO chips. In terms of higher frequency range, RF output, noise and DC features, 20 VCO chips with the thickness of substrates of around 250 µM were characterised before die-substrate thinning. After de-incorporating a cable loss of 1.5 dB, the RF output power was evaluated at 978 MHz. Therefore, for each performance metric, the aggregate of those values is assigned as a reference. In (1), the die-substrate thickness factor (X) is defined so that the effect of a varied die-substrate thickness may be more clearly compared with the RF parameters observed.

$$X = \log(T)/\log(T0) \quad (1)$$

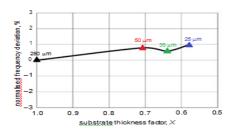

When T is the diameter substrata in  $\mu m$ , and T0 in  $\mu m$  is the default thickness of 250  $\mu m$  in die-substrate. Fig. 3 indicate the standard deviation from the die-substrate thickness factor of VCO chips Fig. 3 (X ). The VCO chip's working frequency is <1% for die-substratum thicken >25  $\mu m$ . It is noticed. The different die-substrate thickness ranges, as illustrated in

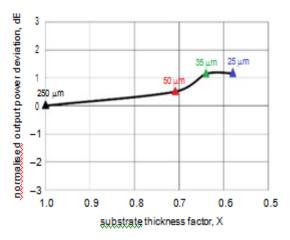

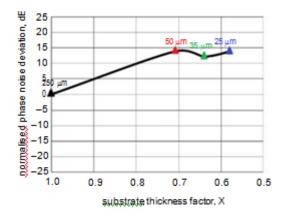

Fig. 4, were examined by applying the tuning voltage of 0-3.5 V. If a substrate thickness is greater than 25 µm, the tuning range for frequency is not much of a help. It is noticed. This figure shows a standardized RF power output deviation of the VCO chips against the X-thickening die-substrate factor. The output rates of the RF are seen to be 0.5 dB higher for the 50 µm, 1 dB higher for 35 µm and 1 dB higher for 25 µm, which shows strong practicality to flexible electronic applications. Fig. 6 shows a phase noise of the various thicknesses of the VCO chips. The divergence from the VCO phase noise with the default die-substrate thickness of 250 μm is found for die-substrate thickness >25 micrometer. This deterioration was considered mostly because the circuit components had a decreased quality factor (Q) as a result of ultra-dilution[6] Phase noise can also be well known to be extremely sensitive to the thickness of the die substrates owing to the leaking of the substrate. Table 1 summarizes the characteristics for different die substratum thicknesses for VCO chips. This indicates that for varied substratum thicknesses the DC parameters reasonably comparable. stav For die-substratum

Relative standard deviation of the VCO and buffer drain currents for 20, 5, 5, and 5 chip samples were recorded at DC parameters of 250, 50, 35, and 25 µm. Five VCO chips were described, with a surface diameter of 15 µm.to reinforce the validity of this reliability study. However, the chips crushed during the characterization during testing, which implies that the thickness of the die substrates is minimal.

Fig. 3 Standard deviation in frequency of the VCO chips vs the thickness factor of the substrates (X)

Fig. 4 VCO frequency tuning band of varied die-substrate thicknesses over tuning voltage

Fig. 5 RF normalised power output divergence from the die-substrate factor of the VCO chips (X)

Fig. 6 Standard noise phase differentiation of VCO chips from thickness factor of the die-substrate (X)

TABLE I. CHARACTERIZATION OF DC ATTRIBUTES FOR VCO CHIPS WITH DIFFERENT DIE-SUBSTRATE THICKNESSES

| Substra<br>te<br>thickness | VCO drain |          | Buffer drain |          |

|----------------------------|-----------|----------|--------------|----------|

|                            | current   |          | current      |          |

|                            | Ave       | Standar  | Ave          | Standar  |

| (µm)                       | rag       | d        | rag          | d        |

| (1111)                     | e         | deviatio | e            | deviatio |

|                            | (m        | n (σ)    | (m           | n (σ)    |

|                            | A)        |          | A)           |          |

| 2                          | 5.08      | 0.       | 19.4         | 0.27     |

| 5                          |           | 13       | 7            |          |

| 0                          |           |          |              |          |

| 5                          | 4.64      | 0.       | 19.7         | 0.17     |

| 0                          |           | 26       | 3            |          |

| 3                          | 4.73      | 0.       | 20.3         | 0.09     |

| 5                          |           | 06       | 0            |          |

| 2                          | 4.50      | 0.       | 19.7         | 0.11     |

| 5                          |           | 10       | 0            |          |

## IV. RESULTS AND DISCUSSION

Below figure shows the schematic implementation of our vco circuit in tanner s-edit

Fig 7 schematic implementation of circuit

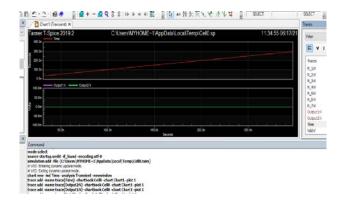

Fig 8 output waveforms of implementation

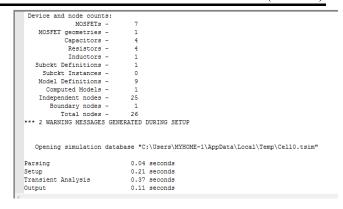

Fig 9 design report

## V. CONCLUSION

Implementation of the CMOS RFIC for ultra-thin, scalable technological circuits is for the first time being accompanied by reliability studies for the first time. Studies were conducted and data was collected in order to find out how die-substrate thinning in a CMOS VCO, designed and fabricated in 180 nm CMOS processes, influences RF efficiencies, RF power output fluctuation, phase noise variation, and DC characteristics. Due to the dilution approach, the VCO's efficiency has been lowered, with the result that the oscillatory frequency and power impacted, have been for control applications in the RFIC, with Wireless Communications. There was major phase noise degradation. At the chip level this must be dealt with either by selecting SOI CMOS where a substratum from the functional circuit isolated or by filling protected dummy metals during RFIC design so that functional structures are more protected against the bulk CMOS substratum.

# (1) References

- [1] Manna, A.L., Guo, W., Huylenbroeck, S.V., et al.: 'Study of 3D process impact on advanced CMOS devices'. 2013 European Microelectronics Packaging Conf. (EMPC), Grenoble, France, September 2013, pp. 1–7

- Chasin, A., Scholz, M., Guo, W., et al.: 'Impact of wafer thinning on front-end reliability for 3D integration'. 2016 IEEE Int. Reliability Physics Symp. (IRPS), Pasadena, CA, USA, April 2016, pp. 6B-2-1-6B-2-6

- [3] Ditali, A., Black, B., Ma, M., et al.: 'A highly reliable DRAM 3-D wafer thinning process'. 2015 IEEE Int. Reliability Physics Symp.,

- Monterey, CA, USA, April 2015, pp. 4C.3.1–4C.3.6

- [4] Premachandran, C.S., Ranjan, R., Agarwal, R., et al.: 'Wafer level high temperature reliability study by backside probing for a 50 μm thin TSV wafer'. Proc. Electronic Components & Technology Conf. (ECTC), San Diego, CA, USA, May 2015, pp. 2144–2148

- [5] Alshahed, M., Yu, Z., Rempp, H., et al.: 'Thermal characterization and modeling of ultra-thin silicon chips'. 2014 44th European Solid State Device Research Conf. (ESSDERC), Venice, Italy, September 2014, pp. 397–400

- [6] Yu, J., Ge, T., He, H., et al.: 'Substrate thickness effect on transformer'. 2016 Int. Symp. on Integrated Circuits (ISIC), Singapore, December 2016, pp. 1–4

- [7] The MOSIS Service. Available at www.mosis.com

- [8] Uniqarta, Inc. Available at www.uniqarta.com

- [9] Roy, P., and Dawn, D.: 'High-power and high-efficiency complementary metal—oxide—semiconductor voltage-controlled oscillator for automatic dependent surveillance-broadcast system', IET Microw. Antennas Propag., 2015, 9, (14), pp. 1632–1637