# DESIGNING OF UART USING VHDL

<sup>1</sup>Renuka Hingmire, <sup>2</sup>Tamanna Jethwa, <sup>3</sup>Aishwarya Askar, <sup>4</sup>Sagar Mahajan, <sup>5</sup>Prashant Shende <sup>1,2,3,4</sup>Student of Electronics and Telecommunication Engineering, <sup>5</sup>Assistant Professor Datta Meghe Institute of Engineering, Technology & Research Salod, Hirapur, Wardha(MS), India.

Abstract: A UART is a device permitting the reception and transmission of statistics in a serial and asynchronous way. In parallel communication the value as well complexity of the gadget will increase because of simultaneous transmission of facts bits on more than one wire. Serial data exchange alleviates this downside of parallel communication and emerges correctly in lots applications for lengthy distance communication as it reduces the signal distortion due to its simple shape. This assignment focuses on the VHDL layout that gives the architecture of UART which reduces parity blunders, framing error, overrun blunders and break error during reception of records through status register. It also permits multiple peripherals to get accessed through single UART.

Index Terms: Asynchronous Serial Transmission, Baud Generator, Status register, Universal Asynchronous Receiver Transmitter.

### I. INTRODUCTION

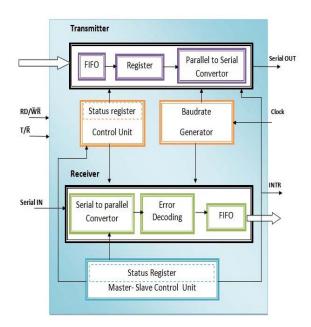

A UART is a device allowing to the transmission and collecting of facts, in a serial. UARTs are utilized for offbeat serial data correspondence via changing over facts from parallel to serial at transmitter with some additional overhead bits utilizing shift register and the opposite way round at beneficiary. Serial ports are moreover used to convey among two computers using a UART as a part of every computer and a hybrid link, which interfaces the transmitter of 1 UART to the collector of the alternative, and the other manner round. The UART consist of transmitter, receiver, baud charge generator and masterslave configuration. The data is dispatched serially, without a clock sign. The primary capability of a

UART is the transformation of parallel-to-serial while transmitting and serial-to-parallel when accepting. The goal defines to interface a couple of fringe devices, to perform this we suggest to utilize Master-Slave association. SPI contain of two portions SPI expert and SPI slave. SPI conference determines 4 sign wires MISOmaster in slave out (yield from slave), MOSImaster out slave in (yield from master), SCLKserial (clock yield from master) and SSslave pick out (dynamic low yield from master). Since the incorporated era is turning into extra complex day by day therefore the hardware descriptive language is becoming popular because it makes easy to layout a circuit of any complexity. Designing the UART we are the use of VHDL makes it clean to understand and read the lavout. simulate and synthesize the design.

## II. DETAILED DESCRIPTION

A. Status Register

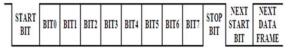

The status sign up is a byte sign in. it's miles utilized for specific detail of casing configuration and fancied baud rate. The equality bits, prevent bits, baud fee desire and word duration may be changed with the aid of composing the right bits in casing function. The transmitter performs parallel-to-serial transformation at the 8-bit facts were given from the CPU. With a specific give up goal 1to synchronize the non concurrent serial information and to protect the statistics uprightness, start, Parity and stop bits are added to the serial statistics. Non concurrent serial correspondence depicts an offbeat transmission conference wherein a start sign is despatched before each byte, individual or code word and a stop sign is despatched after every code word. The start sign serves to set up the getting factor for the collection and enrollment of an image and the stop sign serves to carry the accepting instrument to relaxation in planning for the collection of the following image. an ordinary type of start stop transmission is seemed in fig.1

Fig. 1 UART Frame Format

### B. The UART: How it works

**UART** (Universal Asynchronous Receiver/Transmitter) is the microchip with programming that controls a laptop's interface to its joined serial gadgets. mainly, it furnishes the computer with the RS-232C records Terminal gadget (DTE) interface so it can "communicate" to and change records with modems and different serial gadgets. As a feature of this interface, the UART too: Converts the bytes it receives from the pc along parallel circuits into a solitary serial bit stream circulate for outbound transmission, on inbound transmission, modifications over the serial bit stream circulation into the bytes that the laptop handles, adds an equality bit (in the event selected) on outbound that it is been transmissions and tests the equality approaching bytes (if chosen) and tosses the equality bit, provides start and prevent delineators on outbound and strips them from inbound transmissions, handles hinders from the console and mouse (which might be serial devices with superb ports), might also manage one- of-akind kinds of hinder and gadget administration that require organizing the laptop's price of operation with device speeds.

## C. Asynchronous Serial Transmission

Asynchronous serial conversation describes an asynchronous transmission protocol wherein a preliminary bit is despatched previous to every byte, person or code word and a stop bit is sent after every code word. The start bit serves to put together the receiving technique for the reception and registration of a image and the stop bit serves to convey the receiving technique to relaxation in guidance for the reception of the next symbol. The variety of statistics and formatting bits, and the transmission velocity, ought to be predetermined by the speaking parties. After the forestall bit, the line may also stay idle indefinitely, or every other individual may also straight away be commenced.

### D. Baud Generator

Baud is an estimation of transmission pace in non concurrent correspondence due to propels in modem correspondence innovation, this time period is as often as viable abused whilst portraying the facts costs in extra updated gadgets. normally, a Baud price speaks to the amount of bits which can be virtually being sent over the media, not the measure of statistics that is truely moved from one DTE gadget to the following. The Baud count consists of the overhead bits start, stop and Parity that are created with the aid of the sending UART and uprooted by way of the getting UART.

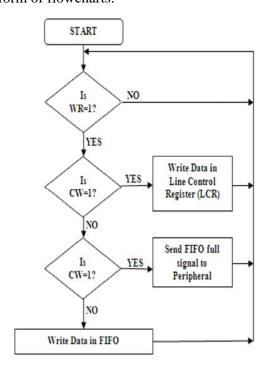

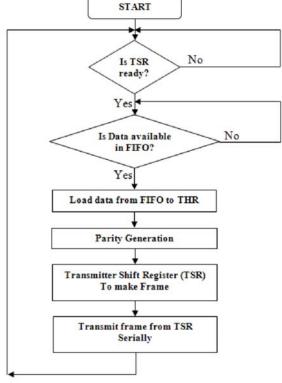

### E. Transmitter

The transmitter area recognizes parallel information, makes the casing of the facts and transmits the records in serial shape at the Transmitter Output terminal. statistics is stacked from the inputs (0-7) into the Transmitter FIFO by using applying reason high at the WR (Write) data within the occasion that words under eight bits are applied, simply the slightest essential bits are transmitted. FIFO is 16-byte check in at the factor whilst FIFO includes a few statistics, it will ship the signal to Transmitter maintain sign up (THR), that's a eight-bit sign in. At a equal time, if THR is void it will send the signal to FIFO, which suggests that THR is prepared to get facts from FIFO. at the off hazard that Transmitter Shift check in (TSR) is void it's going to ship the signal to THR and it demonstrates that TSR is ready to get facts from THR. TSR is a 12-bit sign in in which confining process occurs. In part begin bit, forestall bit and equality bit may be covered. Presently data is transmitted from TSR to TXOUT serially. Fig. 3. and fig.4 demonstrates the whole operating in form of flowcharts.

Fig. 3 Transmitter flowchart (Input to FIFO)

Fig. 4 Transmitter flowchart (FIFO to Output)

#### F.Receiver

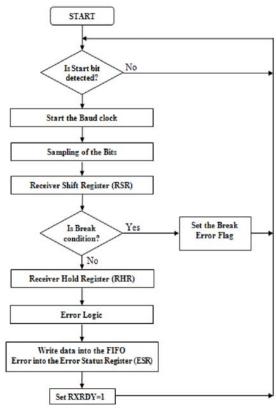

The transmitted records from the transmitter out pin is available at the Receiver terminal (RXIN) pin. The got facts is hooked up to the analyzing motive rectangular. The recipient timing and manipulate is utilized for synchronization of clock sign in the center of transmitter and collector in the beginning the cause line is high at anything factor it is going low checking out and rationale rectangular will take 4 exams of that bit and if each one of the four are identical it demonstrates the start of a casing. After that final bits are inspected further and every one of the bits are send to Receiver Shift sign up (RSR) one after the other where the whole casing is put away. RSR is a 12 bit shift check in presently if the Receiver hold register (RHR) is vacant it sends signal to RSR in order that just the statistics bits from RSR goes to RHR that's a eight bit sign up. The closing bits within the RSR are utilized by the error reason piece, currently if recipient FIFO is void it ship the sign to RHR so that the data bits is going to FIFO. On the factor whilst RD sign is said the records is out there in parallel shape on the RXOUT0-RXOUT7 pins. The blunder intent piece handles four varieties of mistakes: Parity mistake, frame mistake, Overrun mistake, break mistake. inside the occasion that the got equality does not coordinate with the equality constructed from statistics bits PL bit can be set which demonstrates that equality blunder took place. within the event that collector neglects to distinguish proper forestall bit or whilst 4 checks don't coordinate casing mistake occurs and SL bit is ready. at the off hazard that the recipient FIFO is complete and other information lands at the RHR crush blunder happens and OL bit is ready, at the off risk that the RXIN pin is held low for long time than the threshold time then there's a ruin in were given information and destroy blunder takes place and BL bit is set. running of beneficiary is regarded as some distance as flowcharts in fig.5 and fig.6

Fig. 5 Receiver flowchart (Input to FIFO)

Fig. 6 Receiver flowchart (FIFO to Output)

### G. SPI Design

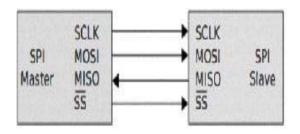

Serial Peripheral Interface is a synchronous convention that permits a master machine to start correspondence with a slave device. records is exchnaged between these gadgets. SPI is completed via system module called as Synchronous Serial Port or the master Synchronous serial port. It lets in serial correspondence among or more devices at a fast and sensibly easy to actualize.

SPI is a Synchronous conference simply the master system can manipulate the clock line,

SCK. Often a slave choose sign will control when a system is gotten to, this sign need to be utilized for whilst multiple slave exist within the framework. This signal is called SS signal and remains for "Slave Select". It indicates to the slave that the professional desires to start a SPI records change among that slave machine and itself.

Fig. 7 SPI Block Diagram

SPI is a serial interface AMD makes use of the following alerts to serially exchange facts with another device: SS This sign is understood as slave select. Whilst it goes low, the slave tool will pay attention for SPI clock and records signals. SCK- that is the serial clock sign. it is generated with the aid of grasp determine and controls while statistics is despatched and when it's miles examine. MOSI- The signals are generated by using master, recipient is the slave. MISO- The signals are generated via slave, recipient is the master. SI- serial information input(used to switch information into the SPI tool). SOSerial information output (used to transfer records out PF the SPI tool). CS- Chip select enter (for permitting device operation). W-Write shield input (used to averse the program/erase commands).

## III. CONCLUSION

From the reported work we are outlining an application that investigate utilization of UART to accomplish advantages like awesome adaptability, minimal effort, superior rationale arrangements furthermore meet correspondence requests rapidly and effectively utilizing

Master-Slave setup. This configuration indicates awesome centrality particularly in the field of electronic outline, where SOC innovation has as of late turned out to be progressively developed. SPI-Interface utilizing Master-Slave to accomplish numerous gadget accesses utilizing a UART.

#### REFERENCES

- [1] S.S.Limaye "VHDL- A Design Oriented Approach", Tata McGrawHill,2008.

- [2] Jayaram Bhaska "VHDL Primer",B S Publication,1991. Hazim Kamal Aansari, Asad Suhail Farooqi."Design of High Speed Uart For Issue 1 Oct Programming FPGA"International Journal Of Engineering And Computer Science, Volume 1, 2012.

- [3] Radha Krishna AN, G. Shruti. "Optimal Implementation design and Simulation of Uart Serial Communication Module Based on Vhdl"International Refereed Journal Of Engineering and Science, Volume 3, Issue 4, April 2014.

- [4] Mohd Yamani Idna Idris,Mashkuri Yaacob,Zaidi Razak,"A VHDL implementation of UART design with BIST capability", Malaysian Journal of Computer Science,Vol. 19(1), 2006.

- [5] Haritha, D.P.Raju "Implementation of multichannel UART with FIFO", International Journal of Advanced Research in Science and Technology, vol. 4, 2015.

- [6] Fang Yi-yuan, Chen Xue-jun."Design and Simulation of UART serial Communication Module Based on VHDL,"Intelligent system and Applications (ISA), 2011 3rd International Workshop on,vol., no.,pp.1-4,28-29 May 2011.

- [7] Sunny Singh, Abhishek Jain and Amanpreet Kaur, Bishwajeet Pandey,"Thermal Aware Low Power Universal Asynchronous Receiver Transmitter Design on FPGA,"Sixth International Conference on Comutational Intelligence and Communication Network,2014 IEEE.

- [8] Naresh Patel, Vatsalkumar Patel and Vikashkumar Patel."VHDL Implementation of UART with Status Register" International Conference on Communication Systems and Network Technologies(IEEE) 2012.

- [9] Roopa M., Vani R.M., P.V.Hunagund "UART Controller as AMBA APB Slave" National Conference on Research & Technology in the Coming Decades, September 2013.

- [10] Ritesh Kumar Agrawal, Vivek Ranjan Mishra "The Design of High Speed UART" Conference on Information and Communication Technologies, June, 2013.

[11] C. E. Cummings,Peter Alfke "Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons", SNUG San Jose, Rev 1.2, 2002.