## AREA-EFFICIENCY AND POWER-DELAY PRODUCT MINIMIZATION IN 64-BIT CARRY SELECT ADDER

Gurpreet kaur<sup>1</sup>, Loveleen Kaur<sup>2</sup>,Navdeep Kaur<sup>3</sup> <sup>1,3</sup>Post graduate student, <sup>2</sup>Assistant Professor, Dept of ECE, BFCET, Bathinda, India Email:<sup>1</sup>gkpreetkaur808@gmail.com,<sup>2</sup>cheemaloveleen@gmail.com, <sup>3</sup>navbrar.kaur@gmail.com

Abstract:In CARRY SELECT ADDER (CSLA) is one of the fastest adder used in manv computers and dataprocessing processors. In this paper, we proposed an area-efficient carry select adder that also having low power consumptions. In this, by sharing the common Boolean logic term, we can reduce the duplicated adder cells that used in the conventional carry select adder. So we only need one XOR gate and one inverter gate for each summation operation as well as one AND gate and one OR gate in each carryout operation. The multiplexers used to select the correct output result according to the logic state of carry-in signal. The proposed 64 bit carry select adder, simulated for 180nm CMOS technologies, has reduced transistor count as well as power delay product reduced than that of conventional carry select adder.

Keywords: carry select adder, area efficient, low power

#### I. INTRODUCTION

In many computers, Digital Signal Processors and other kinds of processors the adder is the most commonly used arithmetic block. Adder is used in the arithmetic logic units, and also in other parts of the processor, where it is used to calculate addresses, table indices, and similar operations. As the adder is mostly used in the Central Processing Unit (CPU) and Digital

Signal Processing (DSP), therefore its performance parameters and power optimization is of utmost importance [4]. Due to the increasing popularity of portable electronic devices the size of the technology is shrinking. At the same time, the power consumption per chip also increases significantly due to the increasing density of the chip. Therefore, in realizing modern Very Large Scale Integration (VLSI) circuits, low-power and high-speed are the predominant factors which need to be considered. Like other circuits' design, the design of high-performance and low-power adders can be addressed at different levels, such as architecture, logic style, layout, and the process technology. As the result, there is always existing a trade-off between the design parameters such as speed, power consumption, and area [6]. Our objective is to design a lowerpower and smaller area as a prime consideration. The ripple carry adder is simple design, but it is the slowest types of adders, carry propagation delay (CPD) is mail concern in this [13].To improve the shortcoming of carry ripple adder to remove the linear dependency between computation delay time, carry select adder is presented [6].

This brief is structured as follow. Section II presents the detailed structure and the function of conventional carry select adder. Section III deals with detailed structure of carry select adder with BEC logic and its functioning. The modified carry select adder by sharing common Boolean logic is described in section IV. Section V contains the simulation results and waveforms. Finally, the work is concluded in section VI.

#### II. Conventional Carry Select Adder

Carry select adder comes in the types of conditional sum adders. Conditional sum adders work on some conditions [4]. A carry-select adder generally consists of two ripple carry adders (RCA) and a multiplexer. Addition of two n-bit numbers with a carry-select adder is done with two ripple carry adders that perform the calculation twice, one time with the assumption of the carry being zero and the other assuming one. When these two results are calculated, the correct sum, and the correct carry, is selected with the multiplexer once the correct carry is known.

The carry select adder divides the ripple carry adder into M parts, while each part consists of a duplicated (N/M)-bit two carry ripple adders. From these two carry ripple adders, one is calculated as carry input value is logic  $-0^{\parallel}$  and another ripple carry adder is calculated as carry input value is logic  $-1^{\parallel}$ . When the actual carry input is ready, either the result of carry input value  $-0^{\parallel}$  path or the result of carry value  $-1^{\parallel}$

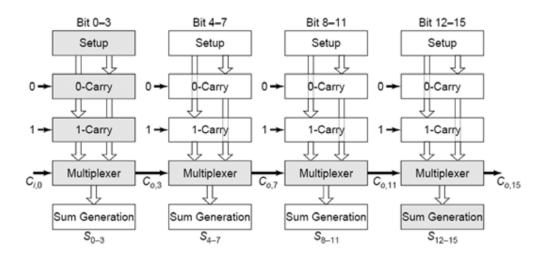

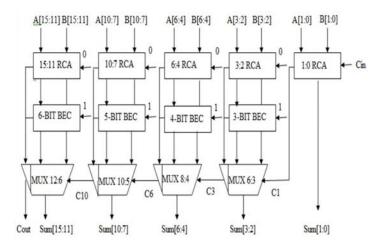

path is selected by the multiplexer according to its correct carry input value [6]. The figure 1 shows 16-bit carry select adder is divided the carry ripple adder into 4 parts, while each part consists of a duplicated 4-bit carry ripple adder pair.

An n-bit Carry select adder consists of \_n' full adders with the carry signal that ripples from one full-adder stage to the next, i.e. from LSB to MSB. It is possible to create a logical circuit using several full adders to add multiple-bit numbers. A C in is the carry input for each full adder which is the C out of the previous adder. Addition of k-bit numbers can be completed in k clock cycles

Fig. 1 The 16-bit carry select adder is divided the carry ripple adder into 4 parts, while each part consists of a duplicated 4-bit carry ripple adder pair.

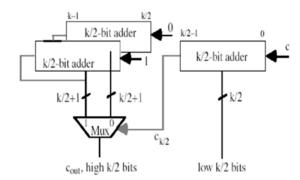

Fig. 2 Block diagram of k-bit adder

#### III. Carry Select Adder with BEC

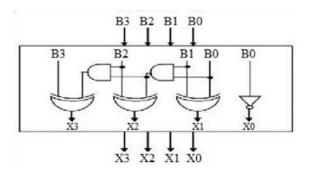

The Binary to Excess one Converter (BEC) replaces the ripple carry adder (RCA) with Cin=1. The main idea of this work is to use BEC instead of the RCA with C in =1 in order to

reduce the area and power consumption of the regular CSLA [8]. BEC uses less number of logic gates than N-bit full adder structure. To replace the n-bit RCA, an n+1 bit BEC is required [12].BEC is a circuit used to add 1 to the input numbers as shown in Fig. 3. Boolean expressions of 4-bit BEC are listed below (Note: symbols ~NOT, &AND and ^XOR) X0= ~B0

$X1 = B0^{B1}$

$X2 = B2^{(B0\&B1)}$

$X3 = B3^{(B0\&B1\&B2)}$

Therefore, CSA using BEC has low power and less area than conventional CSA. SQRT CSLA

has been chosen for comparison with modified design using BEC as it has more balanced delay, less area and low power. The figure-4 shows block diagram for CSA using BEC. One input to the mux goes from the RCA with Cin=0 and other input from the BEC. Comparing the group 2 of both regular and modified CSLA, it is clear that BEC structure reduces the area and power [9].

#### IV. Area-efficient CSA using Common Boolean Logic

To remove the duplicate adder cells in the conventional CSLA, an area efficient SQRT CSLA is proposed by sharing Common Boolean Logic (CBL) term [12]. Through analysing the truth table of a single-bit full-adder, we can find out that the output of

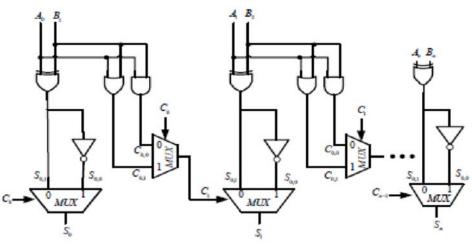

summation signal as carry-in signal is logic  $-0^{\parallel}$  is the inverse signal of itself as carry-in signal is logic  $-1^{\parallel}$ . S0 is  $-0110^{\parallel}$  as Cin is logic  $-0^{\parallel}$  and S0 is  $-1001^{\parallel}$  as Cin is logic "1" [6]. To share the common Boolean logic term, we only need to implement one XOR gate and one INV gate to generate the summation signal pair. As actual carry-in signal is ready, we can select the correct summation output signal according to the logic state of carry-in signal. As for the carry propagation path, we need one OR gate and one AND gate to count possible carry input values in advance. Once the carryin signal is ready, we can select the correct carry-out output according to the logic state of input carry signal. The figure 5 showsareaefficient carry select adder with common Boolean logic sharing.

Table 1: Truth table of one-bit full adder, where the upper part is case of Cin=0 and lower part is the case of Cin=1

| Cin | Α | в | S0   | C0 |

|-----|---|---|------|----|

| 0   | 0 | 0 | 0    | 0  |

| 0   | 0 | 1 | 1    | 0  |

| 0   | 1 | 0 | 1    | 0  |

| 0   | 1 | 1 | 0    | 1  |

| 1   | 0 | 0 |      | 0  |

| 1   | 0 | 1 | 0    | 1  |

| 1   | 1 | 0 | 0    | 1  |

| 1   | 1 | 1 | \ 1/ | 1  |

Fig. 5 Internal structure of the proposed area-efficient carry select adder is constructed by sharing the common

# V. TANNER TOOL SIMULATION RESULTS

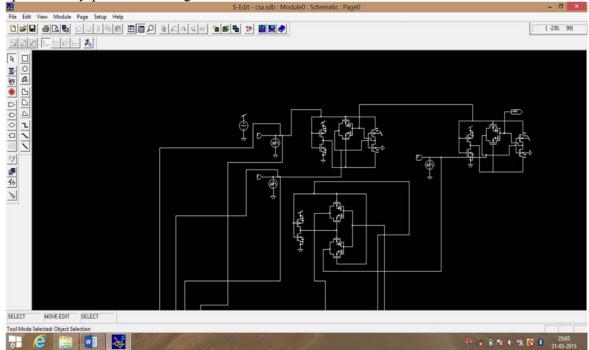

The work has been developed using Tanner Tool version 7. This architecture proposed 64bit carry select adder. The figure 6 shows the schematic diagram for one-bit carry select adder using tanner tool.

The transistor count of our area-efficient carry select adder could be reduced to be very close to that of carry ripple adder, the transistor count in the conventional carry select adder is nearly double as compared with the proposed design. The area-efficient carry select adder achieve an outstanding performance in power consumption. Power consumption can be greatly saved in areaefficient carry select adder

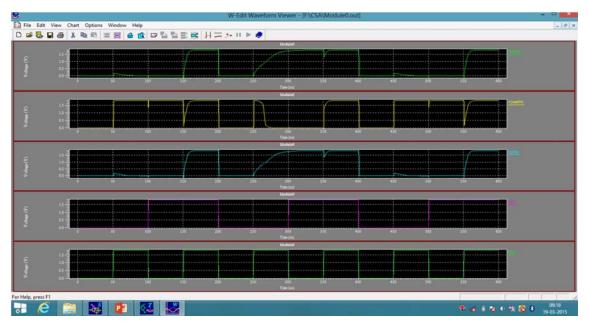

because we only need one XOR gate and one INV gate in each summation operation as well as one AND gate and one OR gate in each carry-out operation after logic simplification and sharing partial circuit. We simulated the power consumption in the proposed areaefficient adder with Common Boolean Logic (CBL), CSA using Binary to Excess-1 Converter (BEC) and the conventional carry select adder with 64-bit in 0.09µm 0.18 µm CMOS technology. The table 2 shows the comparative results analysis for the conventional carry select adder, CSA using BEC and proposed area-efficient carry select adder. The compared results show that the area efficient carry select adder has lees delay, reduced area, lower power consumptions and less power delay product. The figure 7 shows relative output waveforms result for areaefficient carry select adder.

Fig 6 schematic diagram for one bit CSA using tanner tool version 7.

| Design style | Area    | Technology | Avg. power              | Prop. delay            | Power delay |

|--------------|---------|------------|-------------------------|------------------------|-------------|

|              | (No. of | file (µm)  | consumptions(watts)     | at sum (sec)           | Product     |

|              | gate    |            |                         |                        | (pws)       |

|              | count)  |            |                         |                        |             |

| Conventional | 2160    | 0.09       | 95.49 x10 <sup>-3</sup> | 5.19x10 <sup>-</sup>   | 4958.222    |

| CSA          |         |            |                         | 10                     |             |

| CSA using    | 1665    | 0.18       | 79.25x10 <sup>-3</sup>  | 5.40x10 <sup>-10</sup> | 4280.299    |

| BEC          |         |            |                         |                        |             |

| Area-        | 1104    | 0.18       | 5.71x10 <sup>-3</sup>   | 1.62x10 <sup>-10</sup> | 92.502      |

| efficient    |         |            |                         |                        |             |

| CSA(with     |         |            |                         |                        |             |

| CBL)         |         |            |                         |                        |             |

| Area-        | 1104    | 0.09       | 4.96x10 <sup>-3</sup>   | 1.41x10 <sup>-10</sup> | 69.936      |

| efficient    |         |            |                         |                        |             |

| CSA(with     |         |            |                         |                        |             |

| CBL)         |         |            |                         |                        |             |

| Table 2: | simulation     | results  | for area,   | power     | and delay.   |

|----------|----------------|----------|-------------|-----------|--------------|

| 10010    | 01111011011011 | 1.000000 | 101 01 000, | P 0 11 01 | and a stary. |

Fig. 7 simulated waveforms results for sum and carry-out outputs of carry select adder.

### VI. CONCLUSION

In this paper, an area-efficient carry select adder (CSA) is proposed. By sharing the common Boolean logic term, we can remove the duplicated adder cells in the conventional carry select adder. This work presents a simple approach to reduce the area, delay and power of CSLA architecture. The proposed 64 bit carry select adder, simulated for 180nm CMOS technologies using Tanner Tool version 7, and gives much better results than that of conventional carry select adder. The proposed area efficient carry select has lesser transistor count and reduced power delay product which makes it efficient for VLSI hardware implementations.

#### References

[1]Yen-Mou Huang and James B. Kuo,(Oct. 2000) —A High-Speed Conditional Carry Select (CCS) Adder Circuit with a Successively Incremented Carry Number Block (SICNB) Structure for Low-Voltage VLSI Implementation IEEE transactions on circuits and systems—II: Analog and Digital Signal Processing, VOL. 47, NO. 10.

[2] AmauryNève, Helmut Schettler, Thomas Ludwig, and Denis Flandre, (March 2004) —Power-Delay Product Minimization in High-Performance 64-bit Carry-Select Adders IEEE transactions on very large scale integration (VLSI) systems, VOL. 12, NO. 3. [3] BehnamAmelifard ,FarzanFallah Fujitsu and MassoudPedram, (March 2005) —Closing the Gap between Carry Select adderand Ripple Carry Adder: A New Class of Lowpower Highperformance Addersl, IEEE, pp. 148-152.

[4] Padma Devi, AshimaGirdher, and Balwinder Singh (june 2010) —Improved Carry Select Adder with Reduced Area and Low Power Consumption∥ International Journal of Computer Applications (0975 – 8887) Volume 3 – No.4,

[5]B. Ramkumar, and Harish M Kittur (feb. 2012) —Low-Power and Area-Efficient Carry

Select Adder IEEE transactions on very large scale integration (VLSI) systems, VOL. 20, NO. 2.

[6]I-Chyn Wey, Cheng-Chen Ho, YiSheng Lin, and Chien-Chang Peng (march 2012) —An Area-Efficient Carry Select Adder Design by Sharing the Common Boolean Logic Term International MultiConference of Engineers and Computer Scientists, Vol. II.

[7] DeepthiObul Reddy, P. Ramesh Yadav (aug. 2012) —Carry Select Adder with Low Power and Area Efficiency International Journal of Engineering Research and Development e-ISSN: 2278-067X, pISSN: 2278-800X, www.ijerd.com Volume 3,

Issue 3 (August 2012), PP. 29-35.

[8]K.Saranya (jan. 2013) —Low Power and Area-Efficient Carry Select Adder<sup>||</sup> International Journal of Soft Computing and Engineering (IJSCE) ISSN: 22312307, Volume-2, Issue-6, January 2013.

[9]Veena V Nair (july 2013) —Modified Low-Power and Area-Efficient Carry Select Adder using D-Latch International Journal of Engineering Science and Innovative Technology (IJESIT) Volume 2, Issue 4.

[10]K.Swarnalatha, S. Mohan Das and P. Uday Kumar (aug 2013) — AN EFFICIENT CARRY SELECT ADDER WITH LESS DELAY AND **REDUCED AREA USING FPGA QUARTUS II** VERILOG DESIGN IInternational Journal of Science, Engineering and Technology Research (IJSETR) Volume Issue 2. 8. [11]LaxmanShanigarapu, Bhavana Ρ. Shrivastava (aug.2013) - Low-Power and High Speed Carry Select Adder International Journal of Scientific and Research Publications, Volume 3, Issue 8, August 2013 1 ISSN 2250-3153.

[12]PallaviSaxena, UrvashiPurohit, Priyanka Joshi (sept. 2013) —Analysis of Low Power, Area- Efficient and High Speed Fast Adder International Journal of Advanced Research in Computer and Communication Engineering Vol. 2, Issue 9.

[13]Basant Kumar Mohanty, Sujit Kumar Patel (june 2014) —Area–Delay–Power Efficient Carry-Select Adderl IEEE transactions on circuits and systems—II: express briefs, VOL. 61, NO. 6.